用于微波电路的单层片式晶界层电容器

摘要:研究了施主掺杂还原气氛烧结的SrTiO3基半导体瓷的组成与性能关系。通过等效电路分析,XRD、SEM 显微结构观察,探讨晶界效应及其特性对瓷料性能作用的机理,从而制成介电系数可调( 10000~50000),电容量变化率低(≤±4.7% ~≤±22%),使用温域宽(﹣55℃~+125℃)的单层片式晶界层电容器瓷片。通过在瓷片上溅射和电镀方法制作电极,并以光刻腐蚀,精密加工成通用型,表面贴装型,多电极型和阵列型的单层片 式电容器,用于微波电路。

关键字:单层片式电容器,晶界层,介电系数,温度特性,系列产品

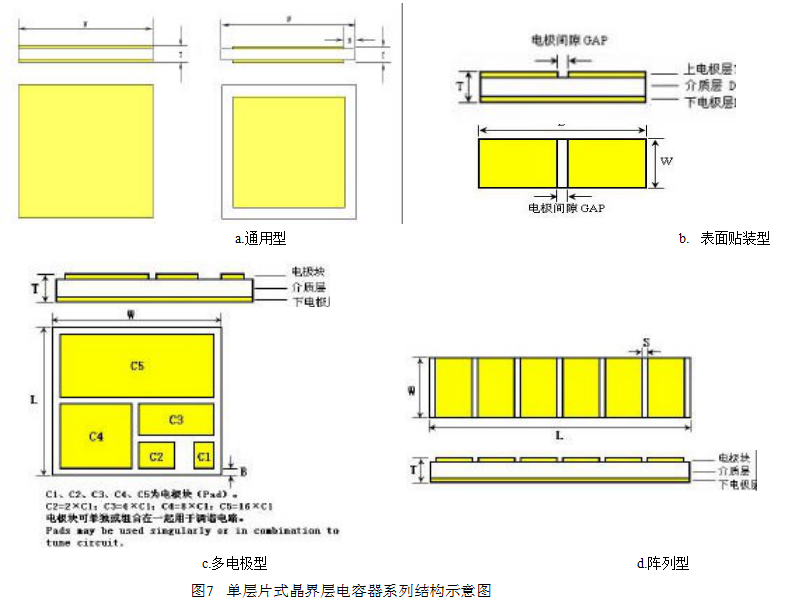

随着现代电子技术的迅速发展,微波在高端民用领域均得到广泛应用,如雷达、导弹遥控, 卫星通讯、定位,电视卫星接收器,无线局域等系统。微波电路中微波集成(MIC),隔直RF旁路,射频旁路,源旁路介,匹配网络,解耦电路等,都需求高精度的电容器。单层片式晶界层电容器(SLBC)具有尺寸微小、电容量大、应用温域宽(﹣55℃~125℃)、电容变化率小(≤±4.7%~≤±22%)、频率特性好等优点,是一类适用于微组装工艺和微波电路的新型电容器品种。研发的单层片式晶界层电容器,采用SrTiO3系陶瓷材料,还原气氛烧结制造半导体瓷,经氧化热处理,溅射和电镀电极,光刻腐蚀,高精度切割等先进工艺技术,获得不同的产品规格:通用型, 表面贴装型,多电极型和阵列型。产品尺寸从0.254× 0.254× 0.127mm~2.29× 2.29×0.254mm系列化,该产品已批量生产,投放市场。

1. 工艺技术与检测方法

以SrTiO3为基添加施主杂质和受主杂质配成晶界层电容器瓷料,用流延或轧膜成型制备膜片,在 N2+H2 还原气氛中烧结成半导体瓷片。瓷体电阻率用2182A NaNoVol METER 6221 DC AND AC CURRENT SOURCE仪测量。经氧化热处理后半导体瓷片成为具有高介电系数的晶界层电容器瓷片。在瓷片上溅射TiW,Ni和Au电极,电镀加厚Au电极,然后切割成各种规格的电容器。用HP4278A电容测量仪测量电容量和介质损耗;4210A Test Chamber 电容温度系数测量仪测量电容温度系数;HP4339A高阻测试仪测量绝缘电阻;34A谐振管测量系统测量等效串联电阻;HP8722C矢量网络分析仪分析介质微波特性;JELJSM 扫描电镜观察半导体瓷的断面形貌;Rigaku D/MAX-B全自动X射线衍射仪进行物相分析。

2. 组分、结构、工艺对晶界层电容器性能的影响

2.1 使半导体瓷片的晶粒具有尽可能低的电阻率,是保证SrTiO3晶界层电容器具有高介电系数和低介质损耗优良性能的重要条件之一。SrTiO3的半导体化,是以施主掺杂加还原气氛(N2+H2)烧结的方式进行。在以SrTiO3为基的主料中,用三价离子(La3+、Y3+ 、Yb3+、Sm3+中的一种或几种)作A位取代,或/和五价离子(Nb5+、Ta5+中的一种)作B位取代的方式进行施主掺杂,生成 LaSr3++ 或/和 NbTi5+施主,一方面提供了导电电子,另一方面施主掺杂使晶格发生畸变,有助于氧脱离晶格点,此时在还原气氛的同时作用下, 氧较易于扩散迁移离开晶格,导致一、二价电离氧空位V0 ×· 、V0 ×·· 缺陷的生成,也提供了导电电子,从而使参与导电的电子数量大大增加;由于SrTiO3中的Ti 为易变价元素,上述的导电电子易于被邻近的Ti4+变价为Ti3+(相当于T i4++e'),此弱束博电子以跳跃(hopping)方式参与导电,从而具有较高的电子迁移率;因两者的同时作用而得到良好的n型半导体化晶粒[1-4]。试验表明,施主掺杂物的添加量与电阻率成U形曲线关系,通过优选施主掺杂量,用四探针法测得半导体瓷片的电阻率可低至0.2~0.5Ω·cm。

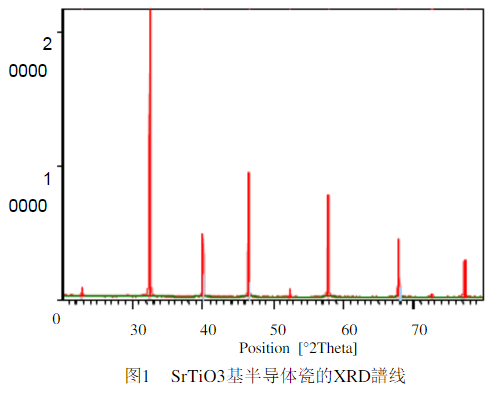

对已半导化的半导体瓷片进行X射线衍射分析,其谱线图如图1;已知未掺杂的SrTiO3晶体为立方结构,而瓷片也呈现为立方结构,只是晶格参数略有变化,这是施主杂质进入晶格取代的结果。

2.2 使瓷片具有适合的晶界层结构,则是保证SrTiO3晶界层电容器具有高介电系数、低介质损耗和小的电容温度变化率的另一重要条件。在瓷料中添加的受主掺杂物和后续工艺中的涂覆物,经烧结和氧化热处理后形成所需的晶界层。晶界层包括由涂覆物形成的第二相绝缘层,以及由氧扩散进入晶粒表层形成的扩散层。绝缘层和扩散层的厚度对视在静态介电系数和电容温度变化率影响极大,薄的晶界层能得到高的介电系数,但低的电容变化率只有在绝缘层与扩散层厚度之间有一合适的比例时才能得到[5、6];因此,一般是通过调整涂覆物含量以及优化热处理工艺,加意控制两层之间的比例,使介电系数和电容温度系数两者的综合性能能满足应用要求为度。研发的两种不同电容器用瓷片的介电系数及其温度特性如图2。

2.3 通过晶粒与晶界层尺寸的不同组合,可调整晶界层电容器的视在静态介电系数 Keff 值。图3为晶界层电容器的等效电路图,绝缘层、扩散层和晶粒的参数分别用下标i、d和g表示。

在角频率x ® 0 的低频情况下,由简化的等效电路,得到 Keff 的计算式(1),其中 s g 为SrTiO3 晶粒的本征介电系数[7]:

由式( 1)可见,晶界层电容器瓷片的晶粒径增大或晶界层厚度减小,都可使dg/(dd+di)比值增大,得到较大的视在介电系数;反之相反。因此,可通过调整瓷料配方组成和工艺技术,使瓷片晶粒大小不同或/和晶界层厚薄不同,以得到不同的介电系数值。当然,这时还必需兼顾到电容温度变化率的要求,为此晶界层内的绝缘层与扩散层之间还必须如2.1中所述,做到合理的组合,以保证介电系数和电容温度变化率两个参数,都能满足应用的要求。

图 中(a )晶粒径约40~60微米,对应的介电系数50000~60000,(b)晶粒径约5~20微米,对应的介电系数8000~12000,此规律与等效电路的分析相符。

2.4 应用于微波频率下的晶界层电容器,仅仅介质损耗低是不够的,还要求电容器的电极和终端金属材料的损耗要小,介质损耗和金属损耗之和用一个等效串联电阻(ESR)的参数表示,即 ESR要小;由于在微波频段,金属的趋肤效应随频率的增加将愈来愈严重, 故降低金属部分的损耗显得尤为重要。采用在瓷片上溅射T i-W ,Ni和Au电极,并辅以电镀加厚Au电极,用光刻技术使电极的结构和布置更为合理等工艺,可使1GHz频率下的ESR值降低至100mΩ以下,不仅具有较小的ESR值,而且其频率特性也比较优良。图 5是用34A谐振管测量系统测得的ESR频率特性。小的ESR值能显著提高微波电路的有效增益,降低插入损耗,延长便携式装置的电池寿命等。

2.5 晶界层电容器在微波频率下工作时,作为电抗元件的寄生参数对微波网络特性的作用和影响,其中特别是应具有尽可能高的自谐振频率这一要求,是元件研发人员需要关注和了解的问题。用HP8722C矢量网络分析仪测量晶界层电容器产品的散射参数S21 值,其频率响应曲线如图6,S21幅值响应出现下凹最低处的频率为元件的并联谐振频率,对图示参数的产品为31.350GHz,是一个相当好的性能指标。电容量大的产品(尺寸相应大),谐振频率低。如电容器在工作频带附近发生并联谐振,它将衰减微波能量,以致元件起不到所希望的作用。因此,电容量选择的上限应保证自谐振频率高于最高使用频率。单层片式晶界层电容器在具有较大电容量的情况下,能有较高的自谐振频率,这与它的视在介电系数高,只需微小尺寸就能获得所需的大电容量,以致寄生串联电感、寄生并联电容数值都大大减小有关。

3. 单层片式晶界层电容器系列

单层片式晶界层电容器系列包括通用型产品,表面贴装型产品,多电极型产品和阵列型产品。各种产品示意图如图7所示。

通用型产品采用微电子组装工艺安装于电路中,其中有留边的产品可以有效避免高温下焊料挥发所导致的短路问题;表面贴装型产品则可适应目前广泛使用的表面贴装工艺,在微波集成电路中取代多层陶瓷电容器;多电极型产品可实现微波环境下的精确调容,主要应用于匹配网络、并联谐振回路、介质谐振器的调谐或耦合;阵列型产品具有集中性高、空间利用率高、组装成本低的优势,应用于解耦电路、射频旁路、砷化镓IC隔直流电路中。

4 结论

4.1 三价或/和五价施主掺杂还原气氛下烧成,经适合的氧化物涂覆及热处理,研制成的SrTiO3晶界层电容器用瓷片,具有介电系数高、介质损耗低、电容温度变化率小等优良性能,可用于制备小体积、大容量而且温度、频率稳定性要求又较高的晶界层电容器。

4.2用溅射、电镀、光刻、精密切割等微细加工手段,可制得最小为0.254×0.254×0.127mm等尺寸系列的单层片式晶界层电容器,以微小尺寸便可得到大的电容量,故自谐振频率高,能满足微波应用的需求。

4.3在瓷片上溅射Ti-W ,Ni和Au电极,并辅以电镀加厚Au电极,用光刻技术使电极的结构和布置更为合理等工艺,有效地降低了等效串联电阻ESR值,而且频率特性优良,有利于提高微波网络的工作性能。

4.4 已生产出单层片式晶界层电容器系列,各型产品可适应微波频率下不同的使用需求。产品性能优良,实现批量生产。

参考文献

[1] 庄严、朱卓雄. Sr/Ti及TiO2晶型对SrTiO3晶界层结构瓷性能的影响.电子元件与材料,2002,21(1):30-34

[2] 曹全喜、周晓华、蔡式东等. SrTiO3陶瓷中掺杂和Ti/Sr的配合.功能材料,1995,26(5):439-441

[3] 徐庆、陈文、严家强等.SrTiO3等系功能陶瓷中一次烧成中的掺杂行为.硅酸盐学报,1997,16(2):21-23

[4] 庄严.SrO-Nb2O5-TiO2系压敏陶瓷中Nb5+ 和Sr2+ 的研究.无机材料学报,2002,17(6):1174-1180

[5] Chung Sung-Yoon, LeeByoung-Ki,Kang Suk-Joong L.

[6] Core-sheii structure in Nb O -doped SrTiO by oxygen partial pressure change . [J] J Am Ceram Soc ,1998,81(11): 3016-3018

[7] 陈志雄、庄严.氧扩散热处理SrTiO3压敏电阻器的非线性和界面势垒.电子元件与材料. 2004,23(9): 11-13,16

[8] 江涛.半导体敏感材料与器件. [M] 广州华南理工大学教材中心 2002,3

上一篇 : 单层芯片电容SLC的发展历史

下一篇 : 单层片式晶界层半导体陶瓷材料研究进展